基於 DSP 中 EMIF 端口的光柵尺數據(jù)采(cǎi)集

2017-8-7 來源:哈爾濱工業大學航天學院 作者:萬勇利(lì) 魏 凱(kǎi) 韓紀曉 陳興林(lín)

摘 要 : 光柵(shān)尺是設(shè)備中常用的位置檢測裝置 , 其測量輸出的(de)信號為數字脈衝 , 具有檢(jiǎn)測範圍大 , 檢測精度高 , 響應(yīng)速度快的特點。C6000 係列 DSP 芯片功耗(hào)低 , 而且具有高性能的處理能力 , 而(ér)且其 EMIF 接口與可以實現與外部存(cún)儲擴展的無縫(féng)連接。本文介紹一(yī)種利用 EMIF 與 FPGA 的無(wú)縫連接 , 實現 DSP 對 FPGA 中存儲的光柵尺數據采集(jí)方(fāng)法。

關鍵詞 :DSP;EMIF;FPGA; 光柵尺 ; 數據采集(jí)

1 引言

DSP 芯片 , 也稱數字信號處理器 , 是一種特別適合(hé)於進行數字信號(hào)處理運算的微處理器 , 其主要應(yīng)用是實時快(kuài)速地(dì)實現各種數字信號處理算法。DSP 有豐富的外設資源 , 其中 EMIF 端口(kǒu)更是滿足了DSP 的(de)外部存(cún)儲擴展和數據交換的需求。通過 EMIF 與外部存儲器連接(jiē)可以實現 DSP 與存儲器的無縫連接(jiē) , 對於數據有更高效的存取速度 , 而且 64 位(wèi)數據線有極高的數據吞吐量。DSP內部對 EMIFA 與 EMIFB 進行了統一編址 , 對 EMIF擴展的存儲空間(jiān)都有相應的地(dì)址映射 , 通過直接訪(fǎng)問相應的地址可以直接獲(huò)得存儲在(zài)外部擴展存儲(chǔ)器中的數據 , 配置好 EMIF 外設後 , 訪(fǎng)問數據十分方便。嵌入式設計中常用作外部 FLASH 擴展、存儲擴展(zhǎn)及和 FPGA數據交換。

光柵尺 , 也稱為光柵尺位移傳感器 , 是利用(yòng)光柵的光學原理工作的測量反(fǎn)饋裝置。光柵尺經常應用於閉環伺服係統中 , 可用作直線位移或者角位移的(de)檢測。其(qí)測量輸出的信號為數(shù)字(zì)脈衝 , 具(jù)有檢測範圍(wéi)大 , 檢測(cè)精度高 , 響應速度(dù)快的特點。利用光柵尺作為位置傳感器可以(yǐ)精確地獲得控製對象的位置信息 , 而且(qiě)光柵尺獲得的數據容易處理(lǐ) , 通過簡單的精度(dù)計算和初始位置選擇就可以得到期望的位置信號。

2 DSP 的 EMIF 端口結(jié)構

本文以 TMS320C64x 係列 DSP 進行說明。DSP 的EMIF 接口支持異步存儲器接口、同步突(tū)發靜(jìng)態存儲器接口和同步動態(tài)存儲器接口 , 支持程序代碼訪問 64 位寬、32 位寬、16 位寬數據訪問。DSP 將(jiāng) EMIF 接 口 分 為 兩 個 部 分 ,EMIFA 和EMIFB, 其中 EMIFA 可以支持(chí) 64 位、32 位、16 位和8 位數據訪問 ,EMIFB 支持 16 位和 8 位數(shù)據(jù)訪問。

DSP 將(jiāng) EMIF 接 口 分 為 兩 個 部 分 ,EMIFA 和EMIFB, 其中 EMIFA 可以支持 64 位、32 位、16 位和(hé)8 位數據訪問 ,EMIFB 支持(chí) 16 位和 8 位數據訪問兩

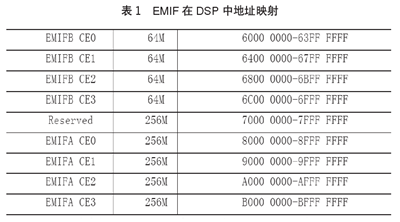

兩個 EMIF 端口(kǒu)的存儲區(qū)均被(bèi)分為 4 個片選空間 , 都可以單獨進行設置與擴展。DSP 對外設 EMIF 端口進行統一編址[1], 其地址映射如表 1 所(suǒ)示(shì)。

從圖(tú)中可以看出 EMIFA 和 EMIFB 分別被分為四個片選區(qū) CE0~CE3, 並且分(fèn)別分配了地址 , 這樣使得 DSP可以同時與不同的存儲器擴展 , 通過訪問不同(tóng)的地址區即可訪問相應的外部存儲器 , 大大提高了 EMIF 端口的設計靈活性又提高了 EMIF 端口的使用效率。EMIF 的端口結構[2]如圖 1 所示。

ECLKIN:EMIF 的外(wài)部時鍾輸入 , 可以作為 EMIF對外輸出時鍾頻(pín)率。

ECLKOUTn:EMIF 對外輸出時鍾頻率(lǜ) , 它的選擇基於 EMIF 的輸入時鍾頻率(1/4 或 1/6 的 DSP 內部時鍾頻率、外(wài)部時鍾(zhōng)頻率)。其中 ECLKOUT1 頻率等(děng)於 EMIF 輸入時(shí)鍾頻(pín)率。ECLKOUT2 可以編程設置為EMIF 輸(shū)入(rù)頻率的 1 倍、1/2 或 1/4。時(shí)鍾頻率的選擇影響外部存儲擴展存儲速度 , 配置 EMIF 需(xū)要注意。

ED:EMIF 的數據線。

EA:EMIF 的地址線。

對(duì)於 EMIF 的外部存儲 , 它的兩個部分 EMIFA 和EMIFB 可以選擇不同的數據位 , 對(duì)於 EMIFA 的外部數(shù)據(jù)線(xiàn)位數選擇[2]。EMIFA 的數(shù)據線(xiàn)可以選擇 64 位 ,32位 ,16 位和 8 位 , 設(shè)計相當的(de)靈活 , 可以根據擴展(zhǎn)的存儲芯片的類(lèi)型進(jìn)行選(xuǎn)擇。EMIFB 的數據線可以(yǐ)選擇16 位和 8 位 , 利用 EMIFB 可以(yǐ)進行低數據外(wài)部存儲的擴展。

EMIFA 常用(yòng)於與外部傳感(gǎn)器(qì)進行大量的數據交換 ,而 EMIFB 則可以(yǐ)用作(zuò) DSP 芯片的 FLASH 芯片擴展及外部 RAM 擴展。兩部分相結合 , 可以滿足數據存儲交換的需求。

3 EMIF 端口與 FPGA 硬件連接設(shè)計

對於 EMIF 端口的引腳我們需要將其與 FPGA 的通用引腳連接起來 , 以(yǐ)便在(zài) FPGA 內進行邏輯編程。其(qí)實 ,對於 FPGA 用作(zuò) EMIF 的存儲用不到(dào)所有的引腳 , 但(dàn)是為了方便以後的設(shè)計(jì)變化 , 我們在原理圖中將 EMIF端口(kǒu)的所有引腳均在 FPGA 中分配了引腳。為了防止沒有用到的 EMIF 引腳的幹擾(rǎo) , 可以將(jiāng)沒有(yǒu)用到的引(yǐn)腳設為高阻態。本設計以 EMIFA 的端口設計(jì)為例進行介紹 ,EMIFB 端口(kǒu)可同樣道理進行設計。在 Altium Designer 軟件中繪製原理圖。圖 3 為與EMIF 端口相關元件圖。左側為 DSP 芯片的(de) EMIF 引腳分布 , 右(yòu)側為 FPGA 與 EMIF 相(xiàng)接管腳。將 DSP 與(yǔ) FPGA 對應管腳相連 , 如圖 2 所示結構。

圖 2 EMIFA 與 FPGA 連接(jiē)圖(tú)

4 DSP 中EMIF 程序配置

在 DSP 中對 EMIF 端口的控製可由 EMIF 對應的寄存器進行配置 , 然(rán)後利用 DSP 的庫函數應用(yòng)配置。以EMIFA端(duān)口配置為例進行介紹。在DSP中有如下宏定義:

#define EMIFA_FMKS(REG,FIELD,SYM)\

_ P E R _ F M K S ( E M I F A , # # R E G , # #

FIELD,##SYM)

此宏定義(yì)可(kě)以實現對於(yú) EMIFA 的 REG 寄存器的FIELD 位賦予 SYM 值。這樣可以(yǐ)方便的對 EMIFA 寄存器進(jìn)行配置(zhì)。對於本設計 ,EMIF 隻要控製好數(shù)據線和地址線及片選使能信(xìn)號、讀寫(xiě)控製信號即可, 其他的配置可以從簡。以下(xià)隻給出本設計的一些關鍵配置 ,其參數可以自(zì)行調節。其他配置位可以根據技術手冊進行設(shè)置。

(1) 對於 ENIF 全局控製寄存器 GBLCTL 配置

E M I F A _ F M K S ( G B L C T L , E K2R A T E , HALFCLK) //ECLKOUT2 輸(shū)出(chū)頻率為 1/2EMIF 輸入(rù)時鍾頻(pín)率。

EMIFA_FMKS(GBLCTL, EK2HZ, CLK) //ECLKOUT2 輸出不間(jiān)斷EMIFA_FMKS(GBLCTL, EK2EN, ENABLE) //ECLKOUT2 輸出使能EMIFA_FMKS(GBLCTL, NOHOLD, DISABLE) // NOHOLD 關閉 ,FPGA 可以發起對 EMIF 總線占有申請。

(2) 對於 ENIFCE 空間控製寄(jì)存器 CECTL 配置

EMIFB_FMKS(CECTL, WRSETUP, OF(2)) // 寫信號到(dào)來前 , 地址線、片選使能先、位使能等信號能建立、讀信號完成後使能芯片需要(yào)兩個時鍾周期。EMIFB_FMKS(CECTL, WRSTRB, OF(6)) // 寫(xiě)信號的寬度為(wéi) 6 個(gè)時鍾周期。EMIFB_FMKS(CECTL, WRHLD, OF(2))

//寫信號到來後對(duì)地址線和字節存儲線(xiàn)占用 2 個時鍾周期。EMIFB_FMKS(CECTL, RDSETUP, OF(2)) //讀信號到來前(qián) , 地址線、片選使能先、位使能等信號能建立、讀信號完成後使能芯片需要兩個時鍾周期。

EMIFB_FMKS(CECTL, RDSTRB, OF(6)) //讀信號的寬度為 6 個(gè)時鍾周期。

EMIFB_FMKS(CECTL, MTYPE, ASYNC64) // 存儲接口為 64 位同步接口。EMIFB_FMKS(CECTL, RDHLD, OF(2)) // 讀(dú)信號到來後對地址線和字節存(cún)儲線占用 2 個時鍾周期。

(3) 其他(tā)寄存器配置

由於本設計沒有使用 SRAM,SDCTL、SDTIM和 S D E X T 默認設置[3]即可。C E S E C 寄存器也保持默認設置。

(4) 利用庫函數應用配置

聲明結構體 EMIFA_Config, 並將配置(zhì)好的寄存器值賦予結構體的各個變量。然後利用(yòng)庫函數void EMIFA_config(EMIFA_Config *config);應用配置即可。

5 光柵尺數據采集設計

光柵尺傳感器的讀數頭(tóu)將讀到的數據匯集到采集卡上 , 采集卡可以實現對多路光柵尺(chǐ)數據的存儲 , 且按一(yī)定的周期刷新各路光柵尺存(cún)儲的(de)數據 , 因(yīn)此 , 我們(men)需要(yào)及時的將采集卡(kǎ)中的各路數據取(qǔ)出,送與DSP運算處理。本(běn)設計采用 FPGA 作為中間(jiān)環節 , 首(shǒu)先將采集卡上采集到的數據存入 FPGA 內部的雙口 RAM 中 ,DSP 再通過EMIF 從 FPGA 的雙(shuāng)口 RAM 中讀取數據。

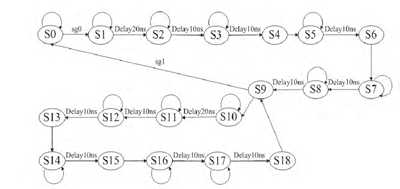

接下來對 FPGA 采集光柵尺數據的邏輯進行設計。由(yóu)於狀態機條理清晰(xī)、運行可靠 , 時序容易把握 , 故本設計采用三段式狀態機進(jìn)行(háng)設計[4][5]。FPGA 對多路光柵尺數據采集的狀(zhuàng)態機的狀態轉移圖如圖 3 所示。

在 S0 狀態 , 判斷 5k Hz 上升沿是否到來 , 用此來(lái)控製讀取光柵(shān)尺數據的周期(qī) , 則周期(qī)為 200us(遠(yuǎn)小於采集卡的(de)刷新周(zhōu)期), 由此決定了 DSP 以 200us 為周期(qī)處理讀到的數據。在 S1 控製發向采集(jí)卡(kǎ)的(de)地(dì)址和發向雙口 RAM 的地址為起始地(dì)址 , 延時 20ns, 等待地址(zhǐ)線穩定。在 S2 狀態(tài) , 將采集卡上得到的數據暫存 , 延時10ns 後 , 在 S3 狀態再次讀取采集卡同一地址的數(shù)據(jù)並暫存 , 通過 S4 狀態(tài)進行數據比較。到 S5, 第三次讀取采集卡同一地址的數據並暫存 ,10ns 延時後 , 在 S6 將三次的數據比較 , 得到中間值並暫存。這樣使得讀數可能存在誤碼率消除 , 係統更(gèng)加穩健。在 S7 狀態將比較的結果(guǒ)放到雙口 RAM 的數據線上 , 並(bìng)且統計讀數次數(shù)為 0。延(yán)時 10ns, 保證數據線的穩定 , 之後在 S8 狀態 , 給雙口(kǒu) RAM 寫信號 , 持續 10ns, 保證數據穩定(dìng)寫入。在(zài) S9 狀態 , 判斷多(duō)路光柵尺數據是否讀完 , 讀完(sg1=1), 則複位 S0 狀態 , 否則進入 S10 狀態。在S10 狀態 , 控製(zhì)發向(xiàng)采集卡的地址和發向雙口 RAM 的地址加 1。S10 到 S18 狀態是對(duì)采集卡上下一路光柵尺數(shù)據的(de)采集 , 原理(lǐ)與前述相同。在 S18 狀態 , 讀取次數加 1, 回到 S9 狀態判斷是否讀取完畢 , 完畢(bì)(sg1=1),則複位 S0, 否(fǒu)則開始(shǐ)下一路光柵尺數據讀取。

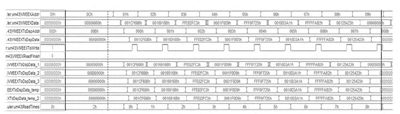

利用 Signal Tap II 對 FPGA 內部邏輯進行監控[6]。可得時序圖(tú)如圖 4 所示。

圖(tú) 中 ,VMEEXAddr 為 FPGA 向 采 集 卡(kǎ) 發 送的地址(zhǐ) ,VMEEXData 為 FPGA 從(cóng)采集卡得到的數據。VMEEXTo Dsp Addr 為 FPGA 發向雙(shuāng)口 RAM的 地 址 ,VMEEXTo Dsp Data 為 FPGA 發 向 雙 口RAM的數據。VMEEXTo Write 為雙口 RAM 寫信(xìn)號。Read Times 為讀取光柵尺的路數 , 從 0 開始。VMEEXTo Dsp Data_1-3 為三次讀取數據(jù)的暫存值。從圖中可以看出在相應的地址內有效地寫入了正確的(de)數據 , 而(ér)且實現了(le)多路(lù)光柵尺數據的讀取 , 時序是正確的。

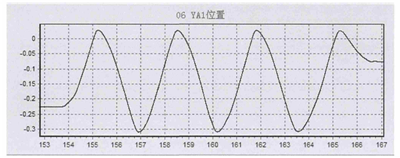

參考圖 1 所示統一編址 , 在 DSP 中訪問相應的 CE片的地址 ,EMIF 可以自動向 FPGA 中設(shè)置的雙口 RAM模塊發送相(xiàng)應地址 , 取得(dé)相應的數據到 DSP, 這樣大(dà)大簡化了訪問外部數據(jù)的步驟(zhòu)而且又很快的速率。通過上位機監視 DSP 中(zhōng)處理得到的電機運行位置信息 , 可得到如圖 5 所示的結果。

圖 3 狀(zhuàng)態機轉移圖

圖 4 光(guāng)柵尺數據采集時(shí)序圖

圖 5 光柵(shān)尺數據采集時序(xù)圖

由圖可見 ,DSP 處理得到了正確的電機位置信息 ,且(qiě)在運動過程中位置變化平滑無毛刺 , 故本設計(jì)達到了正確采集光柵尺數據的要求 , 方案是正確的。

6 結束語

本文設計討論了一種利用 DSP 的 EMIF 讀取多路光柵尺數據的設計方法 , 在實踐中得到良(liáng)好了應用 ,DSP可以準確、可靠地獲(huò)得光(guāng)柵尺傳(chuán)感器返回的電機位置(zhì)信(xìn)號(hào) , 從而為接下來的控製算法打好基礎。在本設計中 , 我們僅討論利用了 DSP 的 EMIFA 端(duān)口 , 對於EMIFB 端口同(tóng)樣可以加以利用 , 可以用來進行 RAM 或FLASH 擴展。設計中 , 利用了 FPGA 作為邏(luó)輯處理的中間(jiān)環節 , 讓其將采集卡的數據(jù)進行存儲 , 這(zhè)樣大大減少了 DSP 的訪(fǎng)問(wèn)壓力。由(yóu)於本文主要針對 TMS32064X係(xì)列 DSP 進行了設計 , 對於不同係列 DSP 的(de) EMIF 配置也有不同 , 故讀者在設(shè)計時需要加以(yǐ)注意。

投稿箱:

如果您有(yǒu)機床行(háng)業、企業相關新(xīn)聞稿件發表,或進行資訊合作,歡迎聯係本網編(biān)輯部, 郵箱:skjcsc@vip.sina.com

如果您有(yǒu)機床行(háng)業、企業相關新(xīn)聞稿件發表,或進行資訊合作,歡迎聯係本網編(biān)輯部, 郵箱:skjcsc@vip.sina.com

更多相關信息

業界視點

| 更多

行業數(shù)據

| 更多

- 2024年(nián)11月 金屬切削機(jī)床產量(liàng)數據

- 2024年11月(yuè) 分地區金屬切削機床產(chǎn)量數(shù)據

- 2024年11月 軸承出口情況

- 2024年11月 基本型乘用車(轎車)產量數據(jù)

- 2024年11月 新能源汽車產量數據

- 2024年11月 新(xīn)能源汽車銷(xiāo)量情況

- 2024年10月 新能源汽車產量數據

- 2024年10月 軸承出(chū)口情況

- 2024年10月 分地區(qū)金屬切削機床產量數(shù)據

- 2024年10月 金屬切削機床產量數據

- 2024年9月 新能源汽(qì)車銷量情況(kuàng)

- 2024年8月 新能源汽車產量(liàng)數據

- 2028年8月 基本型乘用車(轎車)產量數據

博文選(xuǎn)萃(cuì)

| 更多(duō)

- 機械加工過程圖示

- 判斷(duàn)一台加工中心精度的(de)幾種(zhǒng)辦(bàn)法

- 中走絲線切割機床的發展趨勢

- 國產(chǎn)數控係(xì)統和(hé)數控機床何去何(hé)從?

- 中(zhōng)國的技術(shù)工人都去哪裏了?

- 機械老板做了十多年,為(wéi)何還是小作坊?

- 機械行業最新自殺性營銷,害人害(hài)己!不倒(dǎo)閉才

- 製造業大逃亡(wáng)

- 智能(néng)時代,少談點(diǎn)智造,多談點製造(zào)

- 現實麵前,國人(rén)沉(chén)默。製造業的(de)騰(téng)飛,要從機床

- 一文搞懂數控車床加工刀具補償功能

- 車床鑽孔攻螺(luó)紋加工方法及工裝設計

- 傳統鑽削與螺旋(xuán)銑孔加工工藝的區別